Продукти от категория

- FM трансмитер

- 0-50w 50w-1000w 2kw-10kw 10kw +

- TV предавател

- 0-50w 50-1kw 2kw-10kw

- FM антена

- TV Антена

- Антена за аксесоари

- кабел Съединител Мощност Splitter Dummy Заредете

- RF Transistor

- Захранване

- Аудио УРЕДИ

- DTV Front End техника

- Link System

- STL система система Микровълнова Link

- FM радио

- електромера

- Други продукти

- Специален за коронавирус

Продукти Етикети

Fmuser сайтове

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net -> африкаанс

- sq.fmuser.net -> албански

- ar.fmuser.net -> арабски

- hy.fmuser.net -> Арменски

- az.fmuser.net -> азербайджански

- eu.fmuser.net -> баски

- be.fmuser.net -> белоруски

- bg.fmuser.net -> Български

- ca.fmuser.net -> каталунски

- zh-CN.fmuser.net -> китайски (опростен)

- zh-TW.fmuser.net -> Китайски (традиционен)

- hr.fmuser.net -> хърватски

- cs.fmuser.net -> чешки

- da.fmuser.net -> датски

- nl.fmuser.net -> Холандски

- et.fmuser.net -> естонски

- tl.fmuser.net -> филипински

- fi.fmuser.net -> финландски

- fr.fmuser.net -> Френски

- gl.fmuser.net -> галисийски

- ka.fmuser.net -> грузински

- de.fmuser.net -> немски

- el.fmuser.net -> Гръцки

- ht.fmuser.net -> хаитянски креолски

- iw.fmuser.net -> иврит

- hi.fmuser.net -> хинди

- hu.fmuser.net -> Унгарски

- is.fmuser.net -> исландски

- id.fmuser.net -> индонезийски

- ga.fmuser.net -> ирландски

- it.fmuser.net -> Italian

- ja.fmuser.net -> японски

- ko.fmuser.net -> корейски

- lv.fmuser.net -> латвийски

- lt.fmuser.net -> Литовски

- mk.fmuser.net -> македонски

- ms.fmuser.net -> малайски

- mt.fmuser.net -> Малтийски

- no.fmuser.net -> Norwegian

- fa.fmuser.net -> персийски

- pl.fmuser.net -> полски

- pt.fmuser.net -> португалски

- ro.fmuser.net -> Romanian

- ru.fmuser.net -> руски

- sr.fmuser.net -> сръбски

- sk.fmuser.net -> словашки

- sl.fmuser.net -> Словенски

- es.fmuser.net -> испански

- sw.fmuser.net -> суахили

- sv.fmuser.net -> шведски

- th.fmuser.net -> Thai

- tr.fmuser.net -> турски

- uk.fmuser.net -> украински

- ur.fmuser.net -> урду

- vi.fmuser.net -> Виетнамски

- cy.fmuser.net -> уелски

- yi.fmuser.net -> Идиш

Какво е Half Subtractor: Работа и нейните приложения, K-MAP, Схема с помощта на NAND Gate

Date:2021/10/18 21:55:58 Hits:

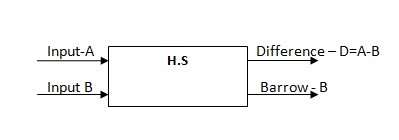

За да обработим информацията като светлина или звук от една точка до друга, можем да използваме аналогови схеми, като даваме подходящи входове под формата на аналогови сигнали. В този процес има шанс за улавяне на шума от входните аналогови сигнали и това може да доведе до загуба на изходния сигнал, което означава, че какъвто и да е вход, който обработваме на входното ниво, не е равен на изходния етап. За да се преодолеят тези цифрови схеми се прилагат. Цифровата схема може да бъде проектирана с логически порти. Логическите порти са електронна схема, която извършва логически операции въз основа на техните входове и дава на изхода само един бит, или нисък (логика 0 = нулево напрежение), или висок (логика 1 = високо напрежение). Комбинираните схеми могат да бъдат проектирани с повече от един логически портал. Тези вериги са бързи и независими от времето без обратна връзка между входа и изхода. Комбинационните схеми са полезни за аритметични и булеви операции. Най -добрите примери за комбинираните схеми включват половин суматор, пълен суматор, половин извадител, пълен извадител, мултиплексори, демултиплексори, енкодер и декодер. Какво е половин извадител? се използва за изваждане на двата бита от входа. Тук изходът на изваждателя зависи изцяло от настоящите входове и не зависи от предишните етапи. Полуизваждащите се резултати са разлика и купчина. Подобно е на артиметичното изваждане, при което ако изваждането е по -голямо от минуса, ще отидем за заем B = 1 или иначе заемът ще остане нула B = 0. За да го разберем по -добре, нека влезем в таблицата на истината, показана по -долу.  полу-изваждаща блок-диаграма Таблицата на истината Таблицата с истината на полу-изваждащата показва стойностите на изхода според входовете, които се прилагат на входните етапи. Таблицата на истината е разделена на две части. Лявата част се обозначава като входен етап, а дясната част се обозначава като изходен етап. В цифровите схеми вход 0 и вход 1 показват ниска логика и висока логика. Според конфигурацията, логически нисък означава нулево напрежение, логическо високо означава високо напрежение (като 5V, 7V, 12V и т.н.). Входове Изходи Вход -AI Вход -B Разлика -DBarrow -B 000010 1001111100 Таблица на истината Обяснение Когато входовете A и B са нула, изходите на полу -извадител D и B също са нула. Когато вход A е висок и B е нула, разликата е висока, т.е. Barrow е нула Когато вход A е нула и вход B е висок, тогава изходите на D и B са високи със съответните. Когато и двата входа са високи, и двата изхода на половин изваждател са нула. От горната таблица на истината можем намерете уравнението за разликата (D) и бароу (B). Уравнения за разлика-D: Разликата е висока, когато входовете A = 1, B = 1 и A = 0, B = 0. От това твърдение D = AB '+A'B = A⊕B. Съгласно уравнението D, той обозначава Ex- или gate.D = A⊕BУравнения за Barrow-B: Баро е висок само когато вход A е нисък, а B е висок. От тази точка уравнението за Barrow B ще бъде, B = A'BB = A'B От горната разлика и уравненията на brow, можем да проектираме схемата на полу -изваждащия, използвайки K -MapK -MapKarnaugh карта опростява израза на булева алгебра за половината верига на изваждащия. Това е официалният метод за намиране на уравнението на булева алгебра за всяка схема. Нека решим булевите изрази за веригата на полу-изваждане, използвайки K-map.K-Map за разлика (D) и Barrow (B)

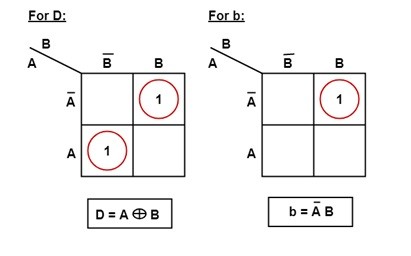

полу-изваждаща блок-диаграма Таблицата на истината Таблицата с истината на полу-изваждащата показва стойностите на изхода според входовете, които се прилагат на входните етапи. Таблицата на истината е разделена на две части. Лявата част се обозначава като входен етап, а дясната част се обозначава като изходен етап. В цифровите схеми вход 0 и вход 1 показват ниска логика и висока логика. Според конфигурацията, логически нисък означава нулево напрежение, логическо високо означава високо напрежение (като 5V, 7V, 12V и т.н.). Входове Изходи Вход -AI Вход -B Разлика -DBarrow -B 000010 1001111100 Таблица на истината Обяснение Когато входовете A и B са нула, изходите на полу -извадител D и B също са нула. Когато вход A е висок и B е нула, разликата е висока, т.е. Barrow е нула Когато вход A е нула и вход B е висок, тогава изходите на D и B са високи със съответните. Когато и двата входа са високи, и двата изхода на половин изваждател са нула. От горната таблица на истината можем намерете уравнението за разликата (D) и бароу (B). Уравнения за разлика-D: Разликата е висока, когато входовете A = 1, B = 1 и A = 0, B = 0. От това твърдение D = AB '+A'B = A⊕B. Съгласно уравнението D, той обозначава Ex- или gate.D = A⊕BУравнения за Barrow-B: Баро е висок само когато вход A е нисък, а B е висок. От тази точка уравнението за Barrow B ще бъде, B = A'BB = A'B От горната разлика и уравненията на brow, можем да проектираме схемата на полу -изваждащия, използвайки K -MapK -MapKarnaugh карта опростява израза на булева алгебра за половината верига на изваждащия. Това е официалният метод за намиране на уравнението на булева алгебра за всяка схема. Нека решим булевите изрази за веригата на полу-изваждане, използвайки K-map.K-Map за разлика (D) и Barrow (B) K-карта за разлика (D) и Barrow (B) Според K-картата първият импликант е A'B, а вторият импликант е AB'. Когато опростяваме това две импликантно уравнение, ще получим опростеното уравнение за разликата на DD = A'B+AB'Тогава, D = A⊕B. Това уравнение просто показва Ex-OR порта. За да намерим опростения булев израз за бароу В, трябва да следваме същия процес, който сме следвали за Разлика D. Следователно, B = A'B. Половин изваждач с помощта на NAND Gates NOR портите се наричат универсални порти. Тук NAND портата се нарича универсална порта, защото можем да проектираме всякакъв вид цифрова схема с използване на n комбинации от номера на NAND порти. Поради тази специалност порта NAND се нарича универсална порта. Сега проектираме верига за полу-изваждане, използвайки NAND порти.

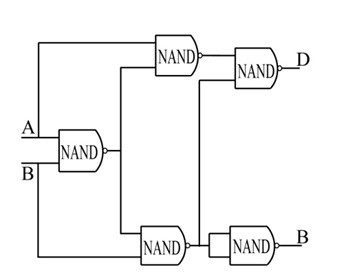

K-карта за разлика (D) и Barrow (B) Според K-картата първият импликант е A'B, а вторият импликант е AB'. Когато опростяваме това две импликантно уравнение, ще получим опростеното уравнение за разликата на DD = A'B+AB'Тогава, D = A⊕B. Това уравнение просто показва Ex-OR порта. За да намерим опростения булев израз за бароу В, трябва да следваме същия процес, който сме следвали за Разлика D. Следователно, B = A'B. Половин изваждач с помощта на NAND Gates NOR портите се наричат универсални порти. Тук NAND портата се нарича универсална порта, защото можем да проектираме всякакъв вид цифрова схема с използване на n комбинации от номера на NAND порти. Поради тази специалност порта NAND се нарича универсална порта. Сега проектираме верига за полу-изваждане, използвайки NAND порти. полу-изваждащ-реализиран-с-NAND-врати Можем да проектираме схемата на полу-изваждащия с пет NAND порта. Разгледайте A и B като входове към първия етап на NAND порта, като неговият изход отново е свързан като един вход към втория NAND порта както и трети NAND порта. Според техните входове, той дава изхода и на последния етап от NAND портите, различният изход D и изходът Browrow ще бъдат на техния изход. Крайното различно D изходно уравнение е D = A ⊕B и уравнение Browrow B като B = A'B. Чрез използване на различна комбинация от NAND порти за конструиране на полуизваждателя, крайните уравнения на разликата и brow ще бъдат само D = A⊕B и B = A'B. на половин извадител Има различни приложения на тези изваждачи. На практика те са лесни за анализ. Някои от тях са изброени по -долу. За да се извадят числата, присъстващи в най -малката позиция в колоните, се предпочитат тези изваждачи. Аритметичната и логическа единица (ALU), присъстваща в процесора, предпочита тази единица за изваждане. За да се сведат до минимум изкривяванията в звука те се използват. Въз основа на необходимата операция половин изваждателят има способността да увеличава или намалява броя на операторите. Половината изваждачи се използват в усилвателя. Докато предават аудио сигналите, те се използват за избягване на изкривяванията. Така че това е всичко Половина изваждаща верига. В условия на реално време изваждането на множество битове не може да се извърши с помощта на полуизваждачи. Този недостатък може да бъде преодолян чрез използване на пълен Subtractor.

полу-изваждащ-реализиран-с-NAND-врати Можем да проектираме схемата на полу-изваждащия с пет NAND порта. Разгледайте A и B като входове към първия етап на NAND порта, като неговият изход отново е свързан като един вход към втория NAND порта както и трети NAND порта. Според техните входове, той дава изхода и на последния етап от NAND портите, различният изход D и изходът Browrow ще бъдат на техния изход. Крайното различно D изходно уравнение е D = A ⊕B и уравнение Browrow B като B = A'B. Чрез използване на различна комбинация от NAND порти за конструиране на полуизваждателя, крайните уравнения на разликата и brow ще бъдат само D = A⊕B и B = A'B. на половин извадител Има различни приложения на тези изваждачи. На практика те са лесни за анализ. Някои от тях са изброени по -долу. За да се извадят числата, присъстващи в най -малката позиция в колоните, се предпочитат тези изваждачи. Аритметичната и логическа единица (ALU), присъстваща в процесора, предпочита тази единица за изваждане. За да се сведат до минимум изкривяванията в звука те се използват. Въз основа на необходимата операция половин изваждателят има способността да увеличава или намалява броя на операторите. Половината изваждачи се използват в усилвателя. Докато предават аудио сигналите, те се използват за избягване на изкривяванията. Така че това е всичко Половина изваждаща верига. В условия на реално време изваждането на множество битове не може да се извърши с помощта на полуизваждачи. Този недостатък може да бъде преодолян чрез използване на пълен Subtractor.

Остави съобщение

Списък на ЛС

Коментари Loading ...