Продукти от категория

- FM трансмитер

- 0-50w 50w-1000w 2kw-10kw 10kw +

- TV предавател

- 0-50w 50-1kw 2kw-10kw

- FM антена

- TV Антена

- Антена за аксесоари

- кабел Съединител Мощност Splitter Dummy Заредете

- RF Transistor

- Захранване

- Аудио УРЕДИ

- DTV Front End техника

- Link System

- STL система система Микровълнова Link

- FM радио

- електромера

- Други продукти

- Специален за коронавирус

Продукти Етикети

Fmuser сайтове

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net -> африкаанс

- sq.fmuser.net -> албански

- ar.fmuser.net -> арабски

- hy.fmuser.net -> Арменски

- az.fmuser.net -> азербайджански

- eu.fmuser.net -> баски

- be.fmuser.net -> белоруски

- bg.fmuser.net -> Български

- ca.fmuser.net -> каталунски

- zh-CN.fmuser.net -> китайски (опростен)

- zh-TW.fmuser.net -> Китайски (традиционен)

- hr.fmuser.net -> хърватски

- cs.fmuser.net -> чешки

- da.fmuser.net -> датски

- nl.fmuser.net -> Холандски

- et.fmuser.net -> естонски

- tl.fmuser.net -> филипински

- fi.fmuser.net -> финландски

- fr.fmuser.net -> Френски

- gl.fmuser.net -> галисийски

- ka.fmuser.net -> грузински

- de.fmuser.net -> немски

- el.fmuser.net -> Гръцки

- ht.fmuser.net -> хаитянски креолски

- iw.fmuser.net -> иврит

- hi.fmuser.net -> хинди

- hu.fmuser.net -> Унгарски

- is.fmuser.net -> исландски

- id.fmuser.net -> индонезийски

- ga.fmuser.net -> ирландски

- it.fmuser.net -> Italian

- ja.fmuser.net -> японски

- ko.fmuser.net -> корейски

- lv.fmuser.net -> латвийски

- lt.fmuser.net -> Литовски

- mk.fmuser.net -> македонски

- ms.fmuser.net -> малайски

- mt.fmuser.net -> Малтийски

- no.fmuser.net -> Norwegian

- fa.fmuser.net -> персийски

- pl.fmuser.net -> полски

- pt.fmuser.net -> португалски

- ro.fmuser.net -> Romanian

- ru.fmuser.net -> руски

- sr.fmuser.net -> сръбски

- sk.fmuser.net -> словашки

- sl.fmuser.net -> Словенски

- es.fmuser.net -> испански

- sw.fmuser.net -> суахили

- sv.fmuser.net -> шведски

- th.fmuser.net -> Thai

- tr.fmuser.net -> турски

- uk.fmuser.net -> украински

- ur.fmuser.net -> урду

- vi.fmuser.net -> Виетнамски

- cy.fmuser.net -> уелски

- yi.fmuser.net -> Идиш

Какво е Hald Adder: Електрическа схема и нейните приложения

Date:2021/10/18 21:55:58 Hits:

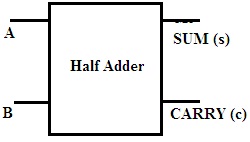

Half Adder е от типа на основната цифрова схема. По-рано има различни операции, извършвани в аналогови схеми. След откриването на цифровата електроника в нея се извършват подобни операции. Цифровите системи се считат за ефективни и надеждни. Сред различните операции една от най-известните операции е аритметиката. Тя включва събиране, изваждане, умножение и деление. Все пак вече е известно, че може да е компютър, всяка електронна джаджа като калкулатор може да извършва математически операции. Тези операции се извършват се състоят от двоични стойности. Това е възможно поради наличието на определени вериги в него. Тези схеми се наричат двоични суматори и изваждащи. Този тип схеми са предназначени за двоични кодове, Excess-3 кодове и други кодове. Други двоични суматори се класифицират в два типа. Те са: Половин суматор и пълен суматор Какво е половин суматор? Цифрова електронна схема, която функционира за извършване на събиране на двоични числа, се дефинира като половин суматор. Процесът на събиране е денар, единствената разлика е избраната бройна система. Съществуват само 0 и 1 в двоичната номерна система. Теглото на числото се основава изцяло на позициите на двоичните цифри. Сред тези 1 и 0, 1 се третира като най-голямата цифра, а 0 като по-малката. Блоковата диаграма на този суматор е Схема на половин суматор Полусуматор Полусуматор се състои от два входа и произвежда два изхода. Смята се за най -простите цифрови схеми. Входовете към тази схема са битовете, върху които трябва да се извърши добавянето. Получените резултати са сумата и носенето.

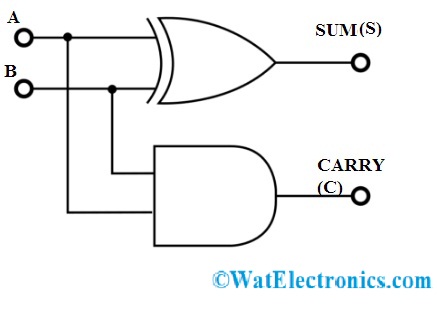

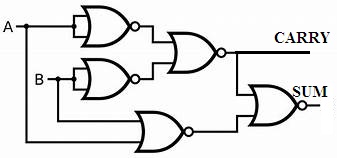

Схема на половин суматор Полусуматор Полусуматор се състои от два входа и произвежда два изхода. Смята се за най -простите цифрови схеми. Входовете към тази схема са битовете, върху които трябва да се извърши добавянето. Получените резултати са сумата и носенето.  Половин суматор Веригата на този суматор се състои от две порти. Те са AND и XOR порти. Приложените входове са еднакви и за двата порта, присъстващи във веригата. Но изходът се взема от всяка порта. Изходът на XOR портата се нарича SUM, а изходът на AND е известен CARRY. Таблица на истината на половината добавител За да се получи връзката на резултата, получен с приложения вход, може да се анализира с помощта на таблица, известна като таблица на истината.

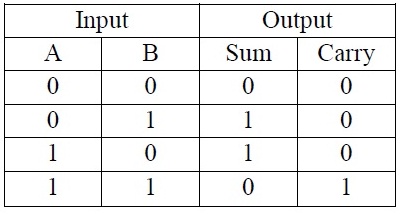

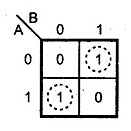

Половин суматор Веригата на този суматор се състои от две порти. Те са AND и XOR порти. Приложените входове са еднакви и за двата порта, присъстващи във веригата. Но изходът се взема от всяка порта. Изходът на XOR портата се нарича SUM, а изходът на AND е известен CARRY. Таблица на истината на половината добавител За да се получи връзката на резултата, получен с приложения вход, може да се анализира с помощта на таблица, известна като таблица на истината. Таблица на истинността на половин суматор От горната таблица на истинността точките са очевидни, както следва: Ако A=0, B=0 това е и двата приложени входа са 0. Тогава и двата изхода SUM и CARRY са 0. Сред два прилагани входа, ако някой е входът е 1, тогава SUM ще бъде e1, но CARRY е 0. Ако и двата входа са 1, тогава SUM ще бъде равен на 0 и CARRY ще бъде равен на 1. Въз основа на приложените входове полусуматорът продължава с операцията Уравнение Уравнението за този тип схеми може да се реализира чрез концепциите за сума от продукти (SOP) и продукти от сума (POS). Булевото уравнение за този тип вериги определя връзката между приложените входове към получените изходи. За определяне на уравнението k-картите се изчертават въз основа на стойностите на таблицата на истинността. Състои се от две уравнения, тъй като в него се използват два логически порта. K-картата на пренасянето е

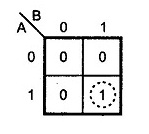

Таблица на истинността на половин суматор От горната таблица на истинността точките са очевидни, както следва: Ако A=0, B=0 това е и двата приложени входа са 0. Тогава и двата изхода SUM и CARRY са 0. Сред два прилагани входа, ако някой е входът е 1, тогава SUM ще бъде e1, но CARRY е 0. Ако и двата входа са 1, тогава SUM ще бъде равен на 0 и CARRY ще бъде равен на 1. Въз основа на приложените входове полусуматорът продължава с операцията Уравнение Уравнението за този тип схеми може да се реализира чрез концепциите за сума от продукти (SOP) и продукти от сума (POS). Булевото уравнение за този тип вериги определя връзката между приложените входове към получените изходи. За определяне на уравнението k-картите се изчертават въз основа на стойностите на таблицата на истинността. Състои се от две уравнения, тъй като в него се използват два логически порта. K-картата на пренасянето е  K-Map AND Gate Изходното уравнение на CARRY се получава от порта AND. C=A.B Булевият израз за SUM се реализира чрез SOP формата. Следователно K-карта за SUM е

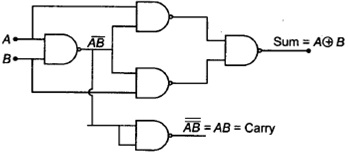

K-Map AND Gate Изходното уравнение на CARRY се получава от порта AND. C=A.B Булевият израз за SUM се реализира чрез SOP формата. Следователно K-карта за SUM е K-Map за Sum (XOR) Определеното уравнение е S= A⊕ BA Приложения Приложенията на този основен суматор са както следва. За извършване на добавяния върху двоични битове, аритметичното и логическото устройство, присъстващо в компютъра, предпочита тази схема на суматор. Комбинацията от схеми на половин суматор води до образуването на веригата за пълен суматор. Тези логически схеми са предпочитани при проектирането на калкулатори. За изчисляване на адресите и таблиците тези схеми са предпочитани. Вместо само събиране, тези схеми са способни да обработват различни приложения в цифрови схеми. Освен това, това се превръща в сърцето на цифровата електроника. VHDL код. VHDL кодът за веригата на Half Adder islibrary ieee;използвайте ieee.std_logic_1164.all;entity half_adder isport(a,b: в бит; sum,carry:out bit);end half_adder ;архитектурните данни на half_adder isbeginsum<= a xor b;carry <= a и b;end data;FAQs1. Какво имате предвид под Adder? Цифровите схеми, чиято единствена цел е да извършват добавяне, са известни като добавки. Това са основните компоненти на ALU. Суматори работят в допълнение към различните формати на числа. Изходите на суматорите са сумата и преноса.2. Какви са ограниченията на половин суматор? Битът за пренасяне, генериран от предишния бит, не може да бъде добавен, е ограничението на този суматор. За да се извърши добавяне за множество битове, тези схеми не могат да бъдат предпочитани. Как да внедрите полусуматор с помощта на NOR Gate? Внедряването на този тип суматор може да се извърши и с помощта на порта NOR. Това е друга универсална порта.

K-Map за Sum (XOR) Определеното уравнение е S= A⊕ BA Приложения Приложенията на този основен суматор са както следва. За извършване на добавяния върху двоични битове, аритметичното и логическото устройство, присъстващо в компютъра, предпочита тази схема на суматор. Комбинацията от схеми на половин суматор води до образуването на веригата за пълен суматор. Тези логически схеми са предпочитани при проектирането на калкулатори. За изчисляване на адресите и таблиците тези схеми са предпочитани. Вместо само събиране, тези схеми са способни да обработват различни приложения в цифрови схеми. Освен това, това се превръща в сърцето на цифровата електроника. VHDL код. VHDL кодът за веригата на Half Adder islibrary ieee;използвайте ieee.std_logic_1164.all;entity half_adder isport(a,b: в бит; sum,carry:out bit);end half_adder ;архитектурните данни на half_adder isbeginsum<= a xor b;carry <= a и b;end data;FAQs1. Какво имате предвид под Adder? Цифровите схеми, чиято единствена цел е да извършват добавяне, са известни като добавки. Това са основните компоненти на ALU. Суматори работят в допълнение към различните формати на числа. Изходите на суматорите са сумата и преноса.2. Какви са ограниченията на половин суматор? Битът за пренасяне, генериран от предишния бит, не може да бъде добавен, е ограничението на този суматор. За да се извърши добавяне за множество битове, тези схеми не могат да бъдат предпочитани. Как да внедрите полусуматор с помощта на NOR Gate? Внедряването на този тип суматор може да се извърши и с помощта на порта NOR. Това е друга универсална порта. Половин суматор, използващ NOR порти4. Как да внедрите Half Adder с помощта на NAND Gate? NAND портата е един от видовете универсални порти. Това показва, че всякакъв вид проектиране на схеми е възможно чрез използването на NAND порти.

Половин суматор, използващ NOR порти4. Как да внедрите Half Adder с помощта на NAND Gate? NAND портата е един от видовете универсални порти. Това показва, че всякакъв вид проектиране на схеми е възможно чрез използването на NAND порти. Half Adder От горната схема, изходът за пренасяне може да бъде генериран чрез прилагане на изхода на един порт NAND към входа като друг порт NAND. Това не е нищо друго освен познато на изхода, получен от порта И. Изходното уравнение на SUM може да бъде генерирано чрез прилагане на изхода на първоначалния порт NAND заедно с отделните входове на A и B към допълнителни NAND порти. И накрая, изходите, получени от тези NAND порти, се прилагат отново към порта. Следователно се генерира изходът за SUM. Следователно основният суматор в цифровата схема може да бъде проектиран чрез използване на различни логически порти. Но добавянето на множество битове става сложно и се счита за ограничение на половин суматор. Можете ли да опишете коя интегрална схема се използва за операцията за нарастване в някакви практически броячи?

Half Adder От горната схема, изходът за пренасяне може да бъде генериран чрез прилагане на изхода на един порт NAND към входа като друг порт NAND. Това не е нищо друго освен познато на изхода, получен от порта И. Изходното уравнение на SUM може да бъде генерирано чрез прилагане на изхода на първоначалния порт NAND заедно с отделните входове на A и B към допълнителни NAND порти. И накрая, изходите, получени от тези NAND порти, се прилагат отново към порта. Следователно се генерира изходът за SUM. Следователно основният суматор в цифровата схема може да бъде проектиран чрез използване на различни логически порти. Но добавянето на множество битове става сложно и се счита за ограничение на половин суматор. Можете ли да опишете коя интегрална схема се използва за операцията за нарастване в някакви практически броячи?

Остави съобщение

Списък на ЛС

Коментари Loading ...