Продукти от категория

- FM трансмитер

- 0-50w 50w-1000w 2kw-10kw 10kw +

- TV предавател

- 0-50w 50-1kw 2kw-10kw

- FM антена

- TV Антена

- Антена за аксесоари

- кабел Съединител Мощност Splitter Dummy Заредете

- RF Transistor

- Захранване

- Аудио УРЕДИ

- DTV Front End техника

- Link System

- STL система система Микровълнова Link

- FM радио

- електромера

- Други продукти

- Специален за коронавирус

Продукти Етикети

Fmuser сайтове

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net -> африкаанс

- sq.fmuser.net -> албански

- ar.fmuser.net -> арабски

- hy.fmuser.net -> Арменски

- az.fmuser.net -> азербайджански

- eu.fmuser.net -> баски

- be.fmuser.net -> белоруски

- bg.fmuser.net -> Български

- ca.fmuser.net -> каталунски

- zh-CN.fmuser.net -> китайски (опростен)

- zh-TW.fmuser.net -> Китайски (традиционен)

- hr.fmuser.net -> хърватски

- cs.fmuser.net -> чешки

- da.fmuser.net -> датски

- nl.fmuser.net -> Холандски

- et.fmuser.net -> естонски

- tl.fmuser.net -> филипински

- fi.fmuser.net -> финландски

- fr.fmuser.net -> Френски

- gl.fmuser.net -> галисийски

- ka.fmuser.net -> грузински

- de.fmuser.net -> немски

- el.fmuser.net -> Гръцки

- ht.fmuser.net -> хаитянски креолски

- iw.fmuser.net -> иврит

- hi.fmuser.net -> хинди

- hu.fmuser.net -> Унгарски

- is.fmuser.net -> исландски

- id.fmuser.net -> индонезийски

- ga.fmuser.net -> ирландски

- it.fmuser.net -> Italian

- ja.fmuser.net -> японски

- ko.fmuser.net -> корейски

- lv.fmuser.net -> латвийски

- lt.fmuser.net -> Литовски

- mk.fmuser.net -> македонски

- ms.fmuser.net -> малайски

- mt.fmuser.net -> Малтийски

- no.fmuser.net -> Norwegian

- fa.fmuser.net -> персийски

- pl.fmuser.net -> полски

- pt.fmuser.net -> португалски

- ro.fmuser.net -> Romanian

- ru.fmuser.net -> руски

- sr.fmuser.net -> сръбски

- sk.fmuser.net -> словашки

- sl.fmuser.net -> Словенски

- es.fmuser.net -> испански

- sw.fmuser.net -> суахили

- sv.fmuser.net -> шведски

- th.fmuser.net -> Thai

- tr.fmuser.net -> турски

- uk.fmuser.net -> украински

- ur.fmuser.net -> урду

- vi.fmuser.net -> Виетнамски

- cy.fmuser.net -> уелски

- yi.fmuser.net -> Идиш

PMOS и NMOS транзистори

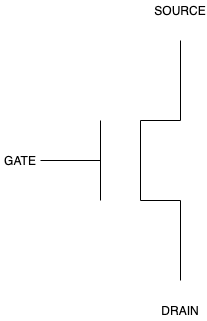

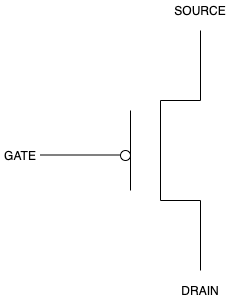

Микропроцесорите са изградени от транзистори. По-специално, те са изградени от MOS транзистори. MOS е акроним за Metal-Oxide Semiconductor. Има два вида MOS транзистори: pMOS (положителен MOS) и nMOS (отрицателен MOS). Всеки pMOS и nMOS е оборудван с три основни компонента: порта, източник и дренаж.

За да разберете правилно как работят pMOS и nMOS, е важно първо да дефинирате някои термини:

затворена верига: Това означава, че електричеството тече от портата към източника.

отворена верига: Това означава, че електричеството не тече от портата към източника; а по-скоро електричеството тече от портата към канализацията.

Когато nMOS транзистор получава напрежение, което не е пренебрежимо, връзката от източника към дренажа действа като проводник. Електричеството ще тече от източника към дренажа без възпрепятстване - това се нарича затворена верига. От друга страна, когато nMOS транзистор получи напрежение от около 0 волта, връзката от източника към дренажа ще бъде прекъсната и това се нарича отворена верига.

Транзисторът p-тип работи точно в противовес на транзистора n-тип. Докато nMOS ще образува затворена верига с източника, когато напрежението не е пренебрежимо малко, pMOS ще образува отворена верига с източника, когато напрежението не е пренебрежимо малко.

Както можете да видите на изображението на pMOS транзистора, показан по-горе, единствената разлика между pMOS транзистор и nMOS транзистор е малкият кръг между портата и първата лента. Този кръг обръща стойността от напрежението; така че, ако портата изпрати напрежение, представително за стойност 1, тогава инверторът ще промени 1 на 0 и ще накара веригата да функционира съответно.

Тъй като pMOS и nMOS функционират по противоположен начин - по допълнителен начин - когато комбинираме и двете в една гигантска MOS верига, тя се нарича cMOS верига, което означава допълнителен метал-оксиден полупроводник.

Използване на MOS схеми

Можем да комбинираме pMOS и nMOS схеми, за да изградим по-сложни структури, наречени GATES, по-точно: логически порти. Вече представихме концепцията за тези логически функции и свързаните с тях таблици на истинност в предишния блог, които можете да намерите, като щракнете върху тук.

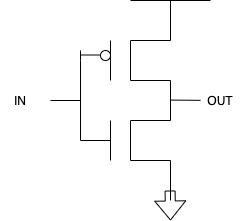

Можем да прикачим pMOS транзистор, който се свързва към източника, и nMOS транзистор, който се свързва със земята. Това ще бъде първият ни пример за cMOS транзистор.

Този cMOS транзистор действа по начин, подобен на логическата функция НЕ.

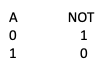

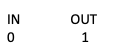

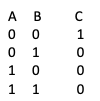

Нека да разгледаме таблицата на истината НЕ:

В таблицата на истината НЕ всяка входна стойност: A се обръща. Какво се случва с горната верига?

Е, нека си представим, че входът е 0.

0 идва и отива както нагоре, така и надолу по проводника към pMOS (отгоре) и nMOS (отдолу). Когато стойността 0 достигне pMOS, тя се обръща на 1; така че връзката с източника е затворена. Това ще произведе логическа стойност от 1, стига връзката със земята (отводняването) също да не е затворена. Е, тъй като транзисторите се допълват, знаем, че nMOS транзисторът няма да обърне стойността; така че той приема стойността 0 такава, каквато е и следователно ще създаде отворена верига към земята (източване). По този начин се получава логическа стойност 1 за портата.

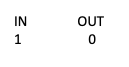

Какво се случва, ако 1 е IN стойността? Е, следвайки същите стъпки, както по-горе, стойността 1 се изпраща както към pMOS, така и към nMOS. Когато стойността бъде получена от pMOS, стойността се обръща на 0; така, връзката с ИЗТОЧНИКА е отворена. Когато стойността е получена от nMOS, стойността не се обръща; по този начин стойността остава 1. Когато стойността 1 бъде получена от nMOS, връзката се затваря; така че връзката със земята е затворена. Това ще произведе логическа стойност от 0.

Събирането на двата набора вход/изход заедно дава:

Доста лесно е да се види, че тази таблица на истинността е абсолютно същата като тази, която логическата функция НЕ произвежда. По този начин това е известно като НЕ порта.

Можем ли да използваме тези два прости транзистора, за да направим по-сложни структури? Абсолютно! След това ще изградим порта NOR и порта OR.

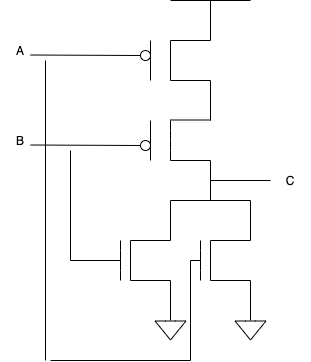

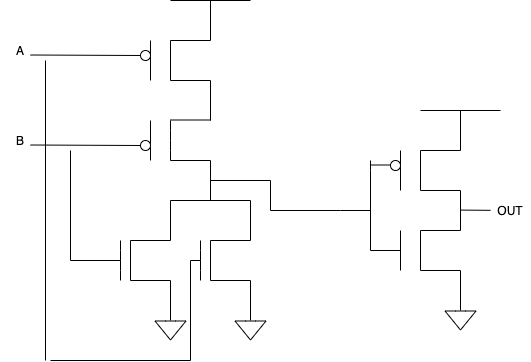

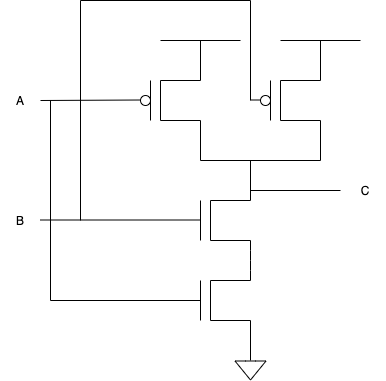

Тази схема използва два pMOS транзистора отгоре и два nMOS транзистора отдолу. Отново, нека разгледаме входа към портата, за да видим как се държи.

Когато A е 0 и B е 0, тази порта ще обърне и двете стойности към 1, когато достигнат pMOS транзисторите; обаче, nMOS транзисторите ще поддържат стойността на 0. Това ще накара портата да произведе стойност от 1.

Когато A е 0 и B е 1, тази порта ще инвертира и двете стойности, когато достигнат pMOS транзисторите; така, A ще се промени на 1 и B ще се промени на 0. Това няма да доведе до източника; тъй като и двата транзистора изискват затворена верига, за да свържат входа към източника. nMOS транзисторите не инвертират стойностите; така, nMOS, свързан с A, ще произведе 0, а nMOS, свързан с B, ще произведе 1; по този начин, nMOS, свързан с B, ще създаде затворена верига към земята. Това ще накара портата да произведе стойност от 0.

Когато A е 1 и B е 0, този порт ще инвертира и двете стойности, когато достигнат pMOS транзисторите; така, A ще се промени на 0 и B ще се промени на 1. Това няма да доведе до източника; тъй като и двата транзистора изискват затворена верига, за да свържат входа към източника. nMOS транзисторите не инвертират стойностите; така, nMOS, свързан с A, ще произведе 1, а nMOS, свързан с B, ще произведе 0; по този начин nMOS, свързан с A, ще създаде затворена верига към земята. Това ще накара портата да произведе стойност от 0.

Когато A е 1 и B е 1, тази порта ще обърне и двете стойности, когато достигнат pMOS транзисторите; така, A ще се промени на 0 и B ще се промени на 0. Това няма да доведе до източник; тъй като и двата транзистора изискват затворена верига, за да свържат входа към източника. nMOS транзисторите не инвертират стойностите; така, nMOS, свързан с A, ще произведе 1, а nMOS, свързан с B, ще произведе 1; по този начин, nMOS, свързан с A и nMOS, свързан с B, ще произведе затворена верига към земята. Това ще накара портата да произведе стойност от 0.

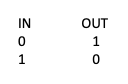

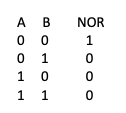

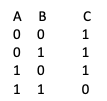

По този начин таблицата на истинността на портата е както следва:

Междувременно таблицата на истинността на логическата функция NOR е както следва:

По този начин ние потвърдихме, че тази порта е порта NOR, защото споделя своята таблица на истинността с логическата функция NOR.

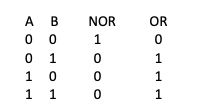

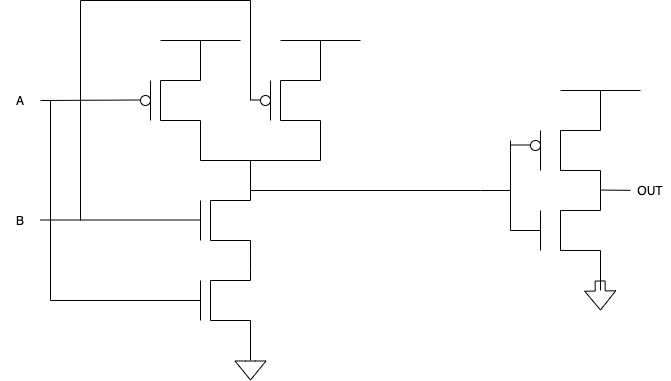

Сега ще съберем и двете порти, които сме създали досега, заедно, за да произведем порта ИЛИ. Не забравяйте, че NOR означава НЕ ИЛИ; така че, ако обърнем вече обърната врата, ще си върнем оригинала. Нека подложим това на тест, за да го видим в действие.

Това, което направихме тук, е, че сме взели NOR порта от преди и приложихме NOT порта към изхода. Както показахме по-горе, портата НЕ ще приеме стойност 1 и ще изведе 0, а портата НЕ ще приеме стойност 0 и ще изведе 1.

Това ще приеме стойностите на порта NOR и ще преобразува всички 0s в 1s и 1s в 0s. Така таблицата на истинността ще бъде както следва:

Ако искате повече практика да тествате тези порти, не се колебайте да изпробвате горните стойности сами и да се уверите, че портата дава еквивалентни резултати!

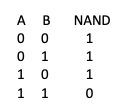

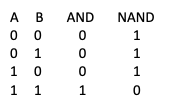

Твърдя, че това е NAND порта, но нека тестваме таблицата на истинността на тази порта, за да определим дали наистина е NAND порта.

Когато A е 0 и B е 0, pMOS на A ще произведе 1, а nMOS на A ще произведе 0; по този начин тази порта ще произведе логическа 1, тъй като е свързана към източника със затворена верига и изключена от земята с отворена верига.

Когато A е 0 и B е 1, pMOS на A ще произведе 1, а nMOS на A ще произведе 0; по този начин тази порта ще произведе логическа 1, тъй като е свързана към източника със затворена верига и изключена от земята с отворена верига.

Когато A е 1 и B е 0, pMOS на B ще произведе 1, а nMOS на B ще произведе 0; по този начин тази порта ще произведе логическа 1, тъй като е свързана към източника със затворена верига и изключена от земята с отворена верига.

Когато A е 1 и B е 1, pMOS на A ще произведе 0, а nMOS на A ще произведе 1; така че трябва да проверим и pMOS и nMOS на B. pMOS на B ще произведе 0, а nMOS на B ще произведе 1; по този начин тази порта ще произведе логическа 0, тъй като е изключена от източника с отворена верига и свързана към земята със затворена верига.

Таблицата на истинността е както следва:

Междувременно таблицата на истинността на логическата функция NAND е както следва:

По този начин ние проверихме, че това наистина е NAND порта.

Сега, как да изградим И порта? Е, ние ще изградим порта И по същия начин, по който построихме порта ИЛИ от порта NOR! Ще закачим инвертор!

Тъй като всичко, което направихме, е да приложим функция НЕ към изхода на портата NAND, таблицата на истината ще изглежда така:

Отново, моля, проверете, за да сте сигурни, че това, което ви казвам, е истината.

Днес разгледахме какво представляват pMOS и nMOS транзистори, както и как да ги използваме за изграждане на по-сложни структури! Надявам се, че сте намерили този блог информативен. Ако искате да прочетете предишните ми блогове, ще намерите списъка по-долу.